# THREE PHASE BRIDGE MOSFET POWER MODULE 3001

M.S.KENNEDY CORP.

4707 Dey Road Liverpool, N.Y. 13088

(315) 701-6751

#### **FEATURES:**

- Pin Compatible with IRFT001

- · P and N Channel MOSFETs for Ease of Drive

- Isolated Package for Direct Heat Sinking, Excellent Thermal Conductivity

- · Avalanche Rated Devices

- · Interfaces Directly with Most Brushless Motor Drive IC's

- 100 Volt, 5 Amp Full Three Phase Bridge at 25°C

#### **DESCRIPTION:**

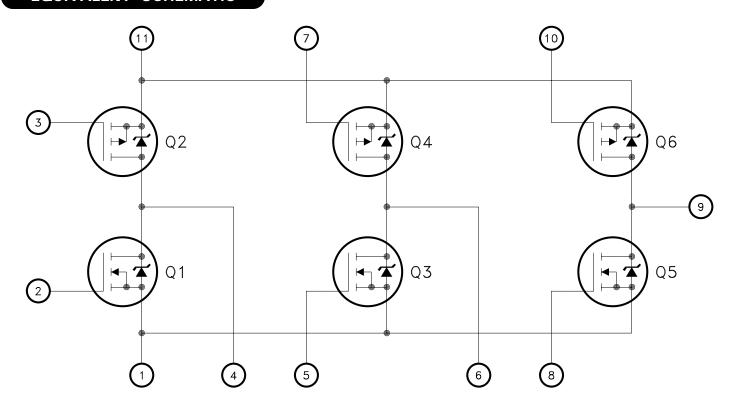

The MSK 3001 is a three phase bridge power circuit packaged in a space efficient isolated ceramic tab power SIP package. Consisting of P-Channel MOSFETs for the top transistors and N-Channel MOSFETs for the bottom transistors, the MSK 3001 will interface directly with most brushless motor drive IC's without special gate driving requirements. The MSK 3001 uses M.S.Kennedy's proven power hybrid technology to bring a cost effective high performance circuit for use in today's sophisticated servo motor and disk drive systems. The MSK 3001 is a replacement for the IRFT001 with only minor differences in mechanical and electrical specifications.

#### **EQUIVALENT SCHEMATIC**

#### TYPICAL APPLICATIONS

- Three Phase Brushless DC Motor Servo Control

- Disk Drive Spindle Control

- · Fin Actuator Control

- · Az-El Antenna Control

### PIN-OUT INFORMATION

Source 1,3,5 1

11 Source 2,4,6

2 Gate 1

3

1

10 Gate 6

Gate 2

9 Drain 5.6

Drain 1,2

8 Gate 5 7 Gate 4

Gate 3 6 Drain 3,4

## **ABSOLUTE MAXIMUM RATINGS**

| VDSS   | Drain to Source Voltage 100V MAX |          | Single Pulse Avalanche Energy                    |

|--------|----------------------------------|----------|--------------------------------------------------|

| VDGDR  | Drain to Gate Voltage            |          | (Q1,Q3,Q5)                                       |

|        | $(RGS = 1M\Omega)$               |          | (Q2,Q4,Q6)                                       |

| Vgs    | Gate to Source Voltage           | ТJ       | Junction Temperature + 175°C MAX                 |

|        | (Continuous) ± 20V MAX           | Тѕт      | Storage Temperature55°C to +150°C                |

| ID     | Continuous Current 5.6A MAX      | Tc       | Case Operating Temperature Range -55°C to +125°C |

| IDM    | Pulsed Current 22A MAX           | $T_{LD}$ | Lead Temperature Range                           |

| RTH-JC | Thermal Resistance               |          | (10 Seconds)                                     |

|        | (Junction to Case) 6°C/W         |          |                                                  |

## **ELECTRICAL SPECIFICATIONS**

| Parameter                          | Test Conditions ④                                        | MSK3001 |      |       |       |

|------------------------------------|----------------------------------------------------------|---------|------|-------|-------|

| i didilictoi                       | Test Conditions 🕁                                        | Min.    | Тур. | Max.  | Units |

| Drain-Source Breakdown Voltage     | Vgs=0 Ip=0.25mA (All Transistors)                        | 100     | -    | -     | V     |

| Durin Communications Communication | Vps=100V Vgs=0V (Q1,Q3,Q5)                               | -       | -    | 25    | μΑ    |

| Drain-Source Leakage Current       | V <sub>DS</sub> = -100V V <sub>GS</sub> = 0V (Q2,Q4,Q6)  | -       | -    | -100  | μΑ    |

| Gate-Source Leakage Current        | $V_{GS} = \pm 20V  V_{DS} = 0  (All Transistors)$        | -       | -    | ± 100 | nA    |

| Cata Carras Threahald Valence      | $V_{DS} = V_{GS} I_{D} = 250 \mu A (Q1,Q3,Q5)$           | 2.0     | -    | 4.0   | V     |

| Gate-Source Threshold Voltage      | $V_{DS} = V_{GS}$ $I_D = 250\mu A (Q2,Q4,Q6)$            | -2.0    | -    | -4.0  | V     |

| Desir Course On Besistants (2)     | Vgs = 10V ID = 5.6A (Q1,Q3,Q5)                           | -       | 0.18 | 0.30  | Ω     |

| Drain-Source On Resistance (2)     | Vgs=-10V ID=-3.4A (Q2,Q4,Q6)                             | -       | 0.37 | 0.75  | Ω     |

| Danier Courses On Brasintana a     | Vgs = 10V ID = 5.6A (Q1,Q3,Q5)                           | -       | -    | 0.21  | Ω     |

| Drain-Source On Resistance ③       | Vgs = 10V ID = -3.4A (Q2,Q4,Q6)                          | -       | -    | 0.60  | Ω     |

|                                    | VDS = 25V ID = 5.7A (Q1,Q3,Q5)                           | 2.7     | -    | -     | S     |

| Forward Transconductance (1)       | V <sub>DS</sub> = -50V I <sub>D</sub> = -3.4A (Q2,Q4,Q6) | 1.5     | -    | -     | S     |

| N-Channel (Q1,Q3,Q5)               |                                                          |         |      |       |       |

| Total Gate Charge ①                | ID = 5.7A                                                | -       | -    | 25    | nC    |

| Gate-Source Charge ①               | V <sub>DS</sub> = 80V                                    | -       | -    | 4.8   | nC    |

| Gate-Drain Charge ①                | Vgs = 10V                                                | -       | -    | 11    | nC    |

| Turn-On Delay Time ①               | V <sub>DD</sub> = 50V                                    | -       | 4.5  | -     | nS    |

| Rise Time ①                        | I <sub>D</sub> = 5.7A                                    | -       | 23   | -     | nS    |

| Turn-Off Delay Time ①              | $R_G = 22\Omega$                                         | -       | 32   | -     | nS    |

| Fall Time ①                        | $R_D = 8.6\Omega$                                        | -       | 23   | -     | nS    |

| Input Capacitance ①                | V <sub>G</sub> s = 0V                                    | -       | 330  | -     | pF    |

| Output Capacitance ①               | V <sub>DS</sub> = 25V                                    | -       | 92   | -     | pF    |

| Reverse Transfer Capacitance ①     | f = 1MHz                                                 | -       | 54   | -     | pF    |

| P-CHANNEL (Q2,Q4,Q6)               |                                                          |         |      |       |       |

| Total Gate Charge ①                | ID = -6.8A                                               | -       | -    | 18    | nC    |

| Gate-Source Charge ①               | V <sub>DS</sub> = -80V                                   | -       | -    | 3.0   | nC    |

| Gate-Drain Charge ①                | Vgs = -10V                                               | -       | -    | 9.0   | nC    |

| Turn-On Delay Time ①               | V <sub>DD</sub> = -50V                                   | -       | 9.6  | -     | nS    |

| Rise Time ①                        | ID = -6.8A                                               | -       | 29   | -     | nS    |

| Turn-Off Delay Time ①              | $R_G = 18\Omega$                                         | -       | 21   | -     | nS    |

| Fall Time ①                        | $R_D = 7.1\Omega$                                        | -       | 25   | -     | nS    |

| Input Capacitance ①                | V <sub>G</sub> s = 0V                                    | -       | 390  | -     | pF    |

| Output Capacitance ①               | V <sub>DS</sub> = -25V                                   | -       | 170  | -     | pF    |

| Reverse Transfer Capacitance ①     | f = 1MHz                                                 | -       | 45   | -     | pF    |

| BODY DIODE                         |                                                          |         |      |       |       |

| Francis On Walters (4)             | Is=5.5A Vgs=0V (Q1,Q3,Q5)                                | -       | 1.3  | -     | V     |

| Forward On Voltage ①               | Is = -5.6A VGS = 0V (Q2,Q4,Q6)                           | -       | -1.6 | -     | V     |

| B B T                              | $Is = 5.7A \text{ di/dt} = 100A/\mu S (Q1,Q3,Q5)$        | -       | 99   | 150   | nS    |

| Reverse Recovery Time ①            | $Is = -6.8A \text{ di/dt} = 100A/\mu S (Q2,Q4,Q6)$       | -       | 100  | 200   | nS    |

| D D C: 0                           | $Is = 5.7A \text{ di/dt} = 100A/\mu S (Q1,Q3,Q5)$        | -       | 0.39 | 0.58  | μC    |

| Reverse Recovery Charge ①          | $Is = -6.8A \text{ di/dt} = 100A/\mu S (Q2,Q4,Q6)$       | -       | 0.33 | 0.66  | μC    |

## **NOTES:**

2

① This parameter is guaranteed by design but need not be tested. Typical parameters are representative of actual device performance but are for reference only. ② Resistance as seen at package pins. ③ Resistance for die only; use for thermal calculations. ④ TA = 25 °C unless otherwise specified. 2 Rev. B 7/

#### N-CHANNEL GATES (Q1,Q3,Q5)

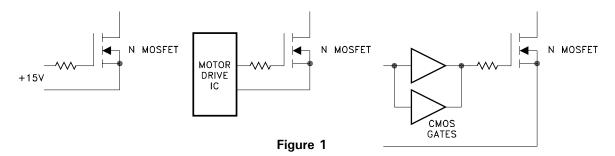

For driving the N-Channel gates, it is important to keep in mind that it is essentially like driving a capacitance to a sufficient voltage to get the channel fully on. Driving the gates to +15 volts with respect to their sources assures that the transistors are on. This will keep the dissipation down to a minimum level [RDS(ON) specified in the data sheet]. How quickly the gate gets turned ON and OFF will determine the dissipation of the transistor while it is transitioning from OFF to ON, and vice-versa. Turning the gate ON and OFF too slow will cause excessive dissipation, while turning it ON and OFF too fast will cause excessive switching noise in the system. It is important to have as low a driving impedance as practical for the size of the transistor. Many motor drive IC's have sufficient gate drive capability for the MSK 3001. If not, paralleled CMOS standard gates will usually be sufficient. A series resistor in the gate circuit slows it down, but also suppresses any ringing caused by stray inductances in the MOSFET circuit. The selection of the resistor is determined by how fast the MOSFET wants to be switched. See Figure 1 for circuit details.

#### P-CHANNEL GATES (Q2,Q4,Q6)

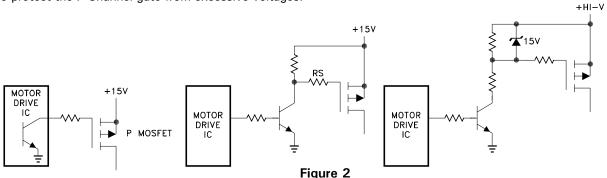

Most everything applies to driving the P-Channel gates as the N-Channel gates. The only difference is that the P-Channel gate to source voltage needs to be negative. Most motor drive IC's are set up with an open collector or drain output for directly interfacing with the P-channel gates. If not, an external common emitter switching transistor configuration (see Figure 2) will turn the P-Channel MOSFET on. All the other rules of MOSFET gate drive apply here. For high supply voltages, additional circuitry must be used to protect the P-Channel gate from excessive voltages.

#### BRIDGE DRIVE CONSIDERATIONS

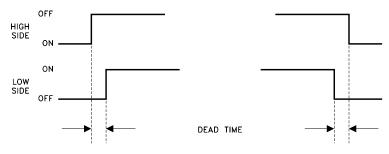

It is important that the logic used to turn ON and OFF the various transistors allow sufficient "dead time" between a high side transistor and its low side transistor to make sure that at no time are they both ON. When they are, this is called "shoot-through", and it places a momentary short across the power supply. This overly stresses the transistors and causes excessive noise as well. See Figure 3.

Figure 3

This deadtime should allow for the turn on and turn off time of the transistors, especially when slowing them down with gate resistors. This situation will be present when switching motor direction, or when sophisticated timing schemes are used for servo systems such as locked antiphase PWM'ing for high bandwidth operation.

## **TYPICAL PERFORMANCE CURVES**

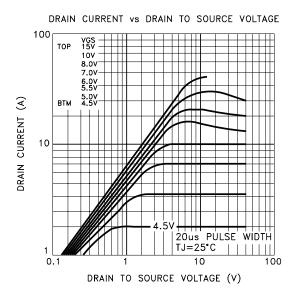

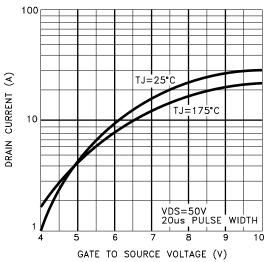

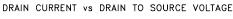

#### N-CHANNEL DEVICES (Q1,Q3,Q5)

#### DRAIN CURRENT vs GATE TO SOURCE VOLTAGE

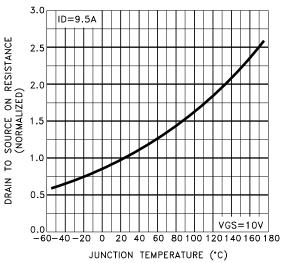

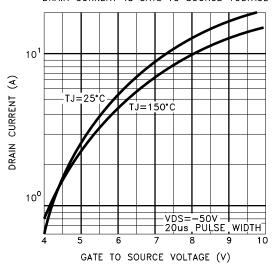

DRAIN TO SOURCE ON RESISTANCE vs JUNCTION TEMP.

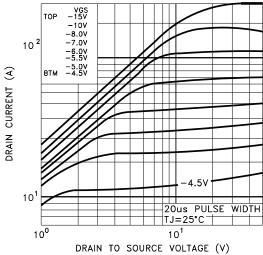

#### P-CHANNEL DEVICES (Q2,Q4,Q6)

DRAIN CURRENT vs GATE TO SOURCE VOLTAGE

DRAIN TO SOURCE ON RESISTANCE vs JUNCTION TEMP.

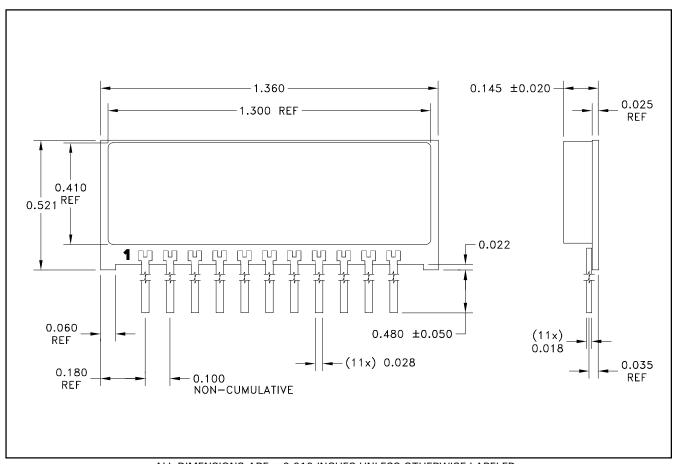

ALL DIMENSIONS ARE  $\pm 0.010$  INCHES UNLESS OTHERWISE LABELED.

## ORDERING INFORMATION

| PART<br>NUMBER | SCREENING LEVEL |  |

|----------------|-----------------|--|

| MSK 3001       | Industrial      |  |

M.S. Kennedy Corp.

4707 Dey Road, Liverpool, New York 13088

Phone (315) 701-6751

FAX (315) 701-6752

www.mskennedy.com

The information contained herein is believed to be accurate at the time of printing. MSK reserves the right to make changes to its products or specifications without notice, however, and assumes no liability for the use of its products.